DS05-20832-3E

# FLASH MEMORY

### CMOS

# 4M (512K × 8) BIT

# MBM29LV004T-12-x/MBM29LV004B-12-x

### FEATURES

- Single 3.0 V read, program, and erase Minimizes system level power requirements

- Compatible with JEDEC-standard commands Uses same software commands as E<sup>2</sup>PROMs

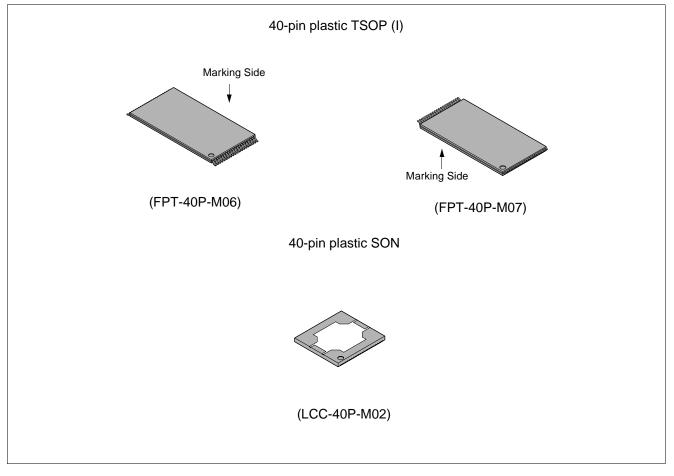

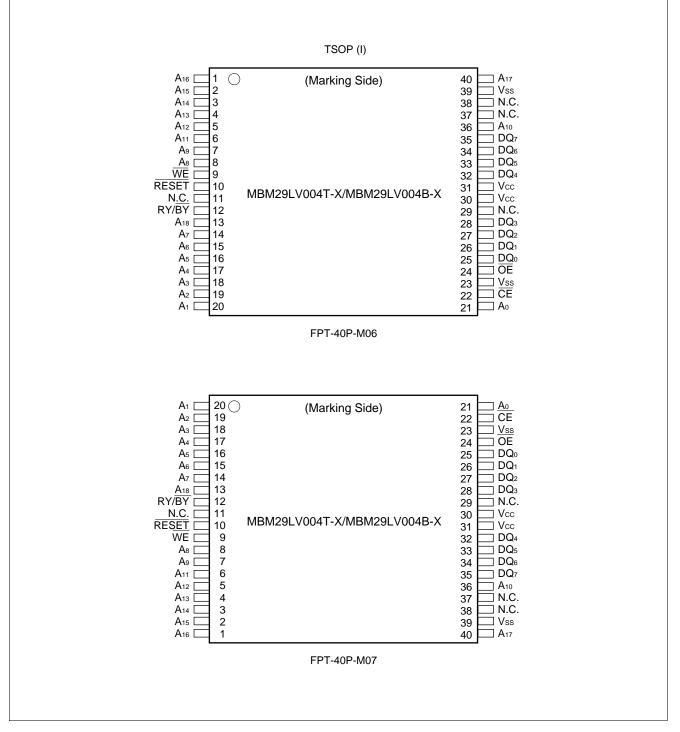

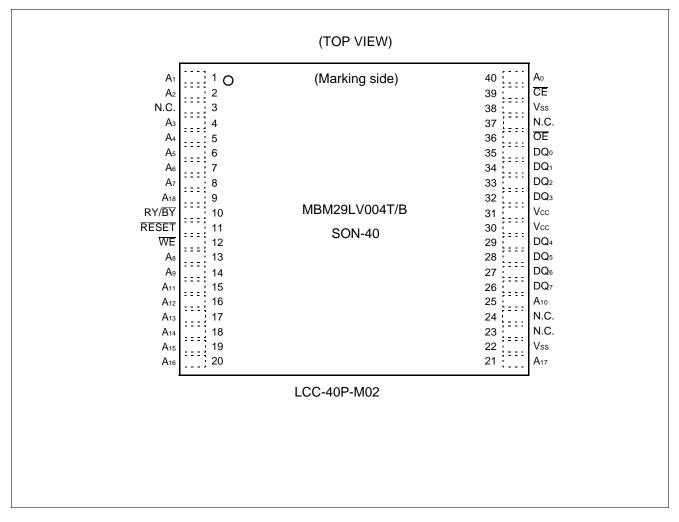

- Compatible with JEDEC-standard world-wide pinouts 40-pin TSOP (Package suffix: PTN – Normal Bend Type, PTR – Reversed Bend Type) 40-pin SON (Package suffix: PNS)

- Minimum 100,000 program/erase cycles

- High performance 120 ns maximum access time

- Sector erase architecture One 16K byte, two 8K bytes, one 32K byte, and seven 64K bytes. Any combination of sectors can be concurrently erased. Also supports full chip erase.

- Boot Code Sector Architecture

- T = Top sector

- B = Bottom sector

- Embedded Erase<sup>™</sup> Algorithms Automatically pre-programs and erases the chip or any sector

- Embedded Program<sup>™</sup> Algorithms Automatically writes and verifies data at specified address

- Data Polling and Toggle Bit feature for detection of program or erase cycle completion

- Ready-Busy output (RY/BY) Hardware method for detection of program or erase cycle completion

- Automatic sleep mode When addresses remain stable, automatically switch themselves to low power mode.

- Low Vcc write inhibit  $\leq$  2.5 V

- Erase Suspend/Resume

- Suspends the erase operation to allow a read in another sector within the same device

- Sector protection Hardware method disables any combination of sectors from program or erase operations.

- Temporary sector unprotection Hardware method enables temporarily any combination of sectors from program or erase operations.

#### (Continued)

Extended operating temperature range; –40°C to +85°C

Please refer to MBM29LV004T/MBM29LV004B data sheet in detailed specifications.

### PACKAGE

#### DESCRIPTION

The MBM29LV004T-X/B-X are a 4M-bit, 3.0 V-only Flash memory organized as 512K bytes of 8 bits each. The MBM29LV004T-X/B-X are offered in 40-pin TSOP (I) and 40-pin SON packages. These devices are designed to be programmed in-system with the standard system 3.0 V Vcc supply. 12.0 V VPP and 5.0 V Vcc are not required for write or erase operations. The devices can also be reprogrammed in standard EPROM programmers.

The standard MBM29LV004T-X/B-X offer access time 120 ns, allowing operation of high-speed microprocessors without wait states. To eliminate bus contention the devices have separate chip enable ( $\overline{CE}$ ), write enable ( $\overline{WE}$ ), and output enable ( $\overline{OE}$ ) controls.

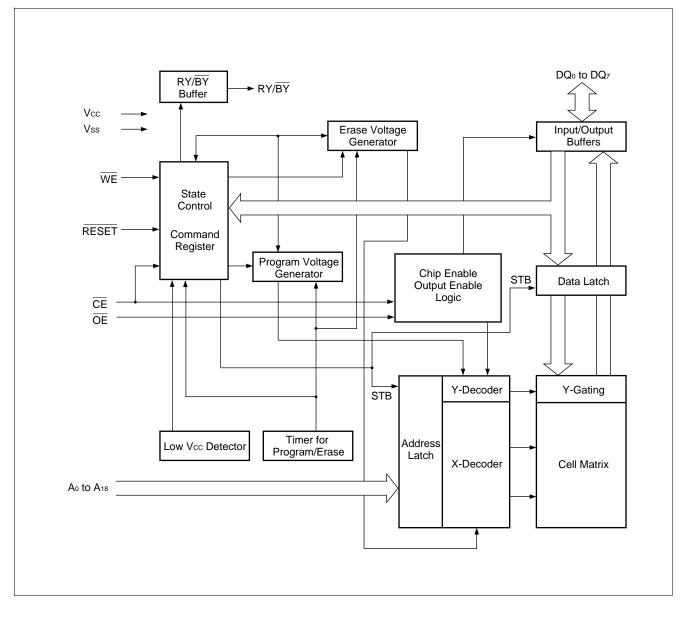

The MBM29LV004T-X/B-X are pin and command set compatible with JEDEC standard E<sup>2</sup>PROMs. Commands are written to the command register using standard microprocessor write timings. Register contents serve as input to an internal state-machine which controls the erase and programming circuitry. Write cycles also internally latch addresses and data needed for the programming and erase operations. Reading data out of the devices is similar to reading from 5.0 V and 12.0 V Flash or EPROM devices.

The MBM29LV004T-X/B-X are programmed by executing the program command sequence. This will invoke the Embedded Program Algorithm which is an internal algorithm that automatically times the program pulse widths and verifies proper cell margin. Typically, each sector can be programmed and verified in about 0.5 seconds. Erase is accomplished by executing the erase command sequence. This will invoke the Embedded Erase Algorithm which is an internal algorithm that automatically preprograms the array if it is not already programmed before executing the erase operation. During erase, the device automatically times the erase pulse widths and verifies proper cell margin.

A sector is typically erased and verified in 1.0 second. (If already completely preprogrammed.)

These devices also feature a sector erase architecture. The sector mode allows each sector to be erased and reprogrammed without affecting other sectors. The MBM29LV004T-X/B-X are erased when shipped from the factory.

The devices feature single 3.0 V power supply operation for both read and write functions. Internally generated and regulated voltages are provided for the program and erase operations. A low V<sub>cc</sub> detector automatically inhibits write operations on the loss of power. The end of program or erase is detected by Data Polling of DQ<sub>7</sub>, by the Toggle Bit feature on DQ<sub>6</sub>, or the RY/BY output pin. Once the end of a program or erase cycle has been completed, the devices internally reset to the read mode.

Fujitsu's Flash technology combines years of EPROM and E<sup>2</sup>PROM experience to produce the highest levels of quality, reliability, and cost effectiveness. The MBM29LV004T-X/B-X memories electrically erase the entire chip or all bits within a sector simultaneously via Fowler-Nordhiem tunneling. The bytes/words are programmed one byte/word at a time using the EPROM programming mechanism of hot electron injection.

### ■ FLEXIBLE SECTOR-ERASE ARCHITECTURE

- One 16K byte, two 8K bytes, one 32K byte, and seven 64K bytes.

- Individual-sector, multiple-sector, or bulk-erase capability.

- Individual or multiple-sector protection is user definable.

|          | 7FFFFH          |

|----------|-----------------|

| 16K byte | 7BFFFH          |

| 8K byte  | 79FFFH          |

| 8K byte  | <i>19</i> FFF11 |

| 32K byte | 77FFFH          |

|          | 6FFFFH          |

| 64K byte | 5FFFFH          |

| 64K byte | 455551          |

| 64K byte | 4FFFFH          |

| 64K byte | 3FFFFH          |

|          | 2FFFFH          |

| 64K byte | 1FFFFH          |

| 64K byte |                 |

| 64K byte | OFFFFH          |

|          | 00000H          |

|          | 7FFFFH |

|----------|--------|

| 64K byte | 6FFFFH |

| 64K byte |        |

| 64K byte | 5FFFFH |

| 64K byte | 4FFFFH |

|          | 3FFFFH |

| 64K byte | 2FFFFH |

| 64K byte | 1FFFFH |

| 64K byte |        |

| 32K byte | OFFFFH |

|          | 07FFFH |

| 8K byte  | 05FFFH |

| 8K byte  | 03FFFH |

| 16K byte |        |

|          | 00000H |

MBM29LV004T-X Sector Architecture

MBM29LV004B-X Sector Architecture

#### ■ PRODUCT LINE UP

| Part No.                      | MBM29LV004T-X/MBM29LV004B-X |

|-------------------------------|-----------------------------|

| Ordering Part No.             | -12                         |

| Max. Address Access Time (ns) | 120                         |

| Max. CE Access Time (ns)      | 120                         |

| Max. OE Access Time (ns)      | 50                          |

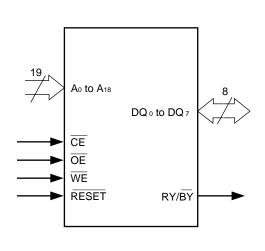

### BLOCK DIAGRAM

### CONNECTION DIAGRAMS

(Continued)

#### (Continued)

### ■ LOGIC SYMBOL

| Table 1                            | WBWI29LV0041/004B PIN Configuration         |

|------------------------------------|---------------------------------------------|

| Pin                                | Function                                    |

| A <sub>0</sub> to A <sub>18</sub>  | Address Inputs                              |

| DQ <sub>0</sub> to DQ <sub>7</sub> | Data Inputs/Outputs                         |

| CE                                 | Chip Enable                                 |

| OE                                 | Output Enable                               |

| WE                                 | Write Enable                                |

| RY/BY                              | Ready-Busy Outputs                          |

| RESET                              | Hardware Reset Pin/Sector Protection Unlock |

| N.C.                               | No Internal Connection                      |

| Vss                                | Device Ground                               |

| Vcc                                | Device Power Supply                         |

#### Table 1 MBM29LV004T/004B Pin Configuration

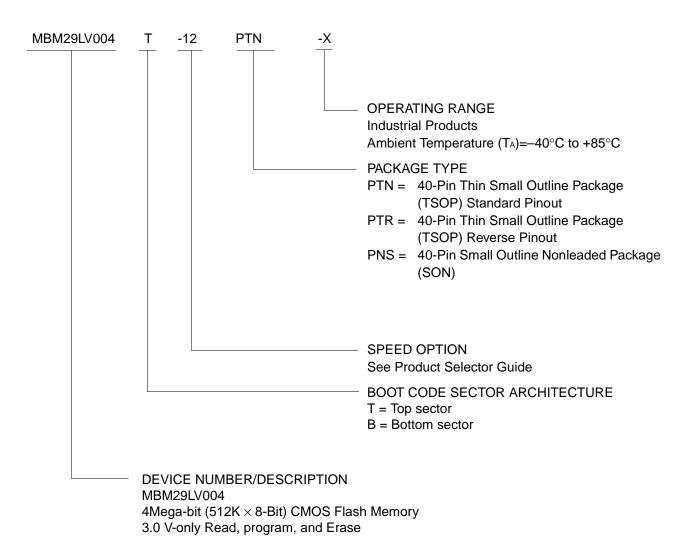

#### ORDERING INFORMATION

#### **Industrial Products**

Fujitsu Industrial products are available in two packages. The order number is formed by a combination of:

### ■ ABSOLUTE MAXIMUM RATINGS

| Storage Temperature                                                                               | –55°C to +125°C             |

|---------------------------------------------------------------------------------------------------|-----------------------------|

| Ambient Temperature with Power Applied                                                            | –40°C to +85°C              |

| Voltage with Respect to Ground All pins except $A_9$ , $\overline{OE}$ , and $\overline{RESET}$ ( | Note 1)–0.5 V to +Vcc+0.5 V |

| Vcc (Note 1)                                                                                      | –0.5 V to +5.5 V            |

| A9, OE, and RESET (Note 2)                                                                        | –0.5 V to +13.0 V           |

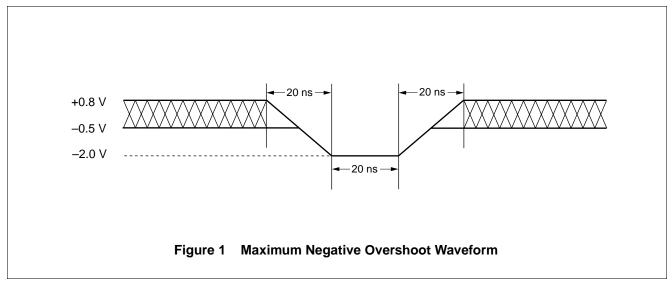

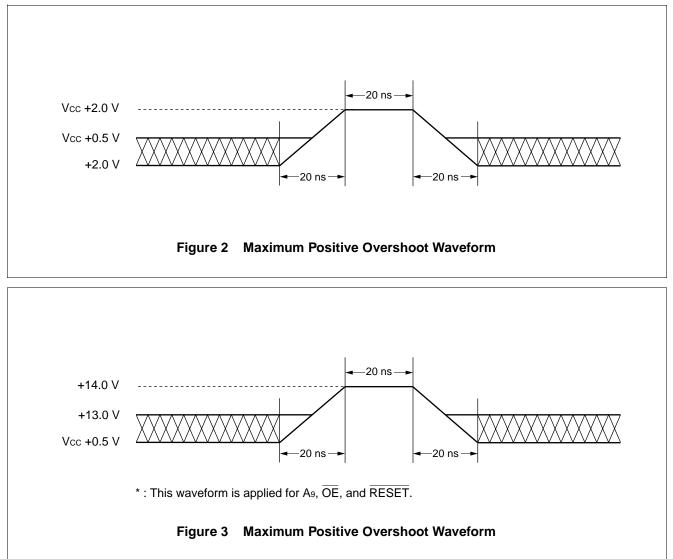

- Notes: 1. Minimum DC voltage on input or I/O pins are -0.5 V. During voltage transitions, inputs may negative overshoot Vss to -2.0 V for periods of up to 20 ns. Maximum DC voltage on output and I/O pins are Vcc +0.5 V. During voltage transitions, outputs may positive overshoot to Vcc +2.0 V for periods of up to 20 ns.

- 2. Minimum DC input voltage on A<sub>9</sub>, OE, and RESET pins are -0.5 V. During voltage transitions, A<sub>9</sub>, OE, and RESET pins may negative overshoot V<sub>SS</sub> to -2.0 V for periods of up to 20 ns. Maximum DC input voltage on A<sub>9</sub>, OE, and RESET pins are +13.0 V which may positive overshoot to 14.0 V for periods of up to 20 ns.

- **WARNING:** Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

### RECOMMENDED OPERATING RANGES

| Industrial Devices                    |                  |

|---------------------------------------|------------------|

| Ambient Temperature (T <sub>A</sub> ) | 40°C to +85°C    |

| Vcc Supply Voltages                   | +2.7 V to +3.6 V |

Operating ranges define those limits between which the functionality of the devices are guaranteed.

**WARNING:** Recommended operating conditions are normal operating ranges for the semiconductor device. All the device's electrical characteristics are warranted when operated within these ranges.

Always use semiconductor devices within the recommended operating conditions. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representative beforehand.

#### MAXIMUM OVERSHOOT

### ■ DC CHARACTERISTICS

| Parameter<br>Symbol | Parameter Description                                                        | Test Conditions                                                                               | Min.      | Max.      | Unit |

|---------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------|-----------|------|

| lu                  | Input Leakage Current                                                        | V <sub>IN</sub> = V <sub>SS</sub> to V <sub>CC</sub> , V <sub>CC</sub> = V <sub>CC</sub> Max. | -1.0      | +1.0      | μA   |

| Ilo                 | Output Leakage Current                                                       | Vout = Vss to Vcc, Vcc = Vcc Max.                                                             | -1.0      | +1.0      | μA   |

| Ιμτ                 | A <sub>9</sub> , OE, RESET<br>Inputs Leakage Current                         | Vcc = Vcc Max.,<br>A <sub>9</sub> , OE, RESET = 12.5 V                                        | _         | 80        | μA   |

| ICC1                | Vcc Active Current (Note 1)                                                  | $\overline{CE} = V_{IL}, \overline{OE} = V_{IH}$                                              | _         | 30        | mA   |

| Icc2                | Vcc Active Current (Note 2)                                                  | $\overline{CE} = V_{IL}, \overline{OE} = V_{IH}$                                              | _         | 35        | mA   |

| Іссз                | Vcc Current (Standby)                                                        | $Vcc = Vcc Max., \overline{CE} = Vcc \pm 0.3 V,$<br>RESET = Vcc ± 0.3 V                       | _         | 50        | μA   |

| ICC4                | Vcc Current (Standby, Reset)                                                 | Vcc = Vcc Max.,<br>RESET = Vss ± 0.3 V                                                        |           | 50        | μA   |

| VIL                 | Input Low Level                                                              | _                                                                                             | -0.5      | 0.6       | V    |

| VIH                 | Input High Level                                                             | _                                                                                             | 2.0       | Vcc + 0.3 | V    |

| VID                 | Voltage for Autoselect and Sector<br>Protection (A <sub>9</sub> , OE, RESET) | _                                                                                             | 11.5      | 12.5      | V    |

| Vol                 | Output Low Voltage Level                                                     | Io∟ = 4.0 mA, Vcc = Vcc Min.                                                                  |           | 0.45      | V    |

| Voh1                | Output Llink Valtage Laug                                                    | Іон = –2.0 mA, Vcc = Vcc Min.                                                                 | 2.4       |           | V    |

| Vон2                | Output High Voltage Level                                                    | Іон = –100 µA, Vcc = Vcc Min.                                                                 | Vcc - 0.4 |           | V    |

| Vlko                | Low Vcc Lock-Out Voltage                                                     | —                                                                                             | 2.3       | 2.5       | V    |

**Notes:** 1. The lcc current listed includes both the DC operating current and the frequency dependent component (at 5 MHz).

The frequency component typically is 2 mA/MHz, with  $\overline{\text{OE}}$  at V\_{IH}.

2. Icc active while Embedded Algorithm (program or erase) is in progress.

### ■ AC CHARACTERISTICS

#### • Read Only Operations Characteristics

| Parameter<br>Symbols |                | Description                                                          | Test Setup                          |          | -12<br>(Note) | Unit |  |

|----------------------|----------------|----------------------------------------------------------------------|-------------------------------------|----------|---------------|------|--|

| JEDEC                | Standard       |                                                                      |                                     | · (Note) |               |      |  |

| tavav                | trc            | Read Cycle Time                                                      | —                                   | Min.     | 120           | ns   |  |

| <b>t</b> ΑνQV        | tacc           | Address to Output Delay                                              | $\frac{\overline{CE}}{OE} = V_{IL}$ | Max.     | 120           | ns   |  |

| <b>t</b> ELQV        | tce            | Chip Enable to Output Delay                                          | <u>OE</u> = Vı∟                     | Max.     | 120           | ns   |  |

| <b>t</b> glqv        | toe            | Output Enable to Output Delay                                        | _                                   | Max.     | 50            | ns   |  |

| <b>t</b> ehqz        | <b>t</b> DF    | Chip Enable to Output High-Z                                         | —                                   | Max.     | 30            | ns   |  |

| t <sub>GHQZ</sub>    | <b>t</b> DF    | Output Enable to Output High-Z                                       | —                                   | Max.     | 30            | ns   |  |

| taxqx                | tон            | Output Hold Time From Addresses,<br>CE or OE, Whichever Occurs First |                                     | Min.     | 0             | ns   |  |

| —                    | <b>t</b> READY | RESET Pin Low to Read Mode                                           | —                                   | Max.     | 20            | μs   |  |

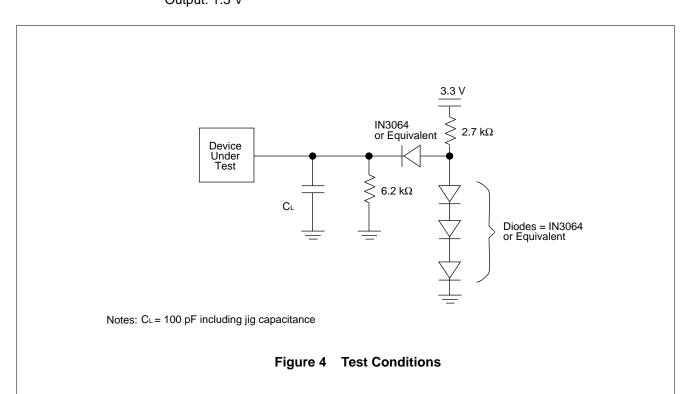

Note: Test Conditions–Output Load: 1 TTL gate and 100 pF Input rise and fall times: 5 ns Input pulse levels: 0.0 V to 3.0 V Timing measurement reference level Input: 1.5 V Output: 1.5 V

#### • Write/Erase/Program Operations Alternate WE Controlled Writes

| Parameter Symbols |                 | Description            |                                              |      | 40  | 11 14 |

|-------------------|-----------------|------------------------|----------------------------------------------|------|-----|-------|

| JEDEC             | Standard        | Description            |                                              |      | -12 | Unit  |

| <b>t</b> avav     | twc             | Write Cycle T          | ime                                          | Min. | 120 | ns    |

| tavwl             | tas             | Address Setu           | p Time                                       | Min. | 0   | ns    |

| <b>t</b> wlax     | tан             | Address Hold           | Time                                         | Min. | 50  | ns    |

| tovwн             | tos             | Data Setup Ti          | me                                           | Min. | 50  | ns    |

| <b>t</b> whdx     | tон             | Data Hold Tim          | ne                                           | Min. | 0   | ns    |

| _                 | toes            | Output Enable          | e Setup Time                                 | Min. | 0   | ns    |

|                   |                 | Output                 | Read                                         | Min. | 0   | ns    |

| _                 | tоен            | Enable Hold<br>Time    | Toggle and Data Polling                      | Min. | 10  | ns    |

| <b>t</b> GHWL     | <b>t</b> GHWL   | Read Recove            | r Time Before Write                          | Min. | 0   | ns    |

| telwl             | tcs             | CE Setup Tim           | le                                           | Min. | 0   | ns    |

| <b>t</b> wheh     | tсн             | CE Hold Time           | CE Hold Time                                 |      | 0   | ns    |

| <b>t</b> wlwh     | twp             | Write Pulse Width      |                                              | Min. | 50  | ns    |

| twнw∟             | twpн            | Write Pulse Width High |                                              | Min. | 30  | ns    |

| twhwh1            | twhwh1          | Byte Program           | ming Operation                               | Тур. | 8   | μs    |

| twhwh2            | twhwh2          | Sector Erase           | Operation (Note 1)                           | Тур. | 1   | sec   |

| _                 | tvcs            | Vcc Setup Tim          | ne                                           | Min. | 50  | μs    |

| _                 | tvlht           | Voltage Trans          | ition Time (Note 2)                          | Min. | 4   | μs    |

| _                 | twpp            | Write Pulse W          | /idth (Note 2)                               | Min. | 10  | μs    |

| _                 | toesp           | OE Setup Tim           | ne to $\overline{\text{WE}}$ Active (Note 2) | Min. | 4   | μs    |

| —                 | <b>t</b> CSP    | CE Setup Tim           | CE Setup Time to WE Active (Note 2)          |      | 4   | μs    |

| _                 | trв             | Recover Time           | Recover Time From RY/BY                      |      | 0   | ns    |

| _                 | t <sub>RP</sub> | RESET Pulse            | RESET Pulse Width                            |      | 500 | ns    |

| _                 | tкн             | RESET Hold             | Time Before Read                             | Min. | 500 | ns    |

|                   | <b>t</b> BUSY   | Program/Eras           | e Valid to RY/BY Delay                       | Min. | 90  | ns    |

Notes: 1. This does not include the preprogramming time.

2. These timings are for Sector Protection operation.

#### • Write/Erase/Program Operations Alternate CE Controlled Writes

| Parameter Symbols |                 | Description             |                             |      | 12  | 11   |

|-------------------|-----------------|-------------------------|-----------------------------|------|-----|------|

| JEDEC             | Standard        | Description             |                             |      | -12 | Unit |

| <b>t</b> avav     | twc             | Write Cycle Time        | )                           | Min. | 120 | ns   |

| <b>t</b> avel     | tas             | Address Setup T         | ïme                         | Min. | 0   | ns   |

| <b>t</b> elax     | tан             | Address Hold Tir        | ne                          | Min. | 50  | ns   |

| <b>t</b> dveh     | tos             | Data Setup Time         | •                           | Min. | 50  | ns   |

| <b>t</b> ehdx     | tdн             | Data Hold Time          |                             | Min. | 0   | ns   |

| _                 | toes            | Output Enable S         | etup Time                   | Min. | 0   | ns   |

|                   | toru            | Output Enable           | Read                        | Min. | 0   | ns   |

|                   | tоен            | Hold Time               | Toggle and Data Polling     | Min. | 10  | ns   |

| <b>t</b> GHEL     | <b>t</b> GHEL   | Read Recover T          | me Before Write             | Min. | 0   | ns   |

| twlel             | tws             | WE Setup Time           |                             | Min. | 0   | ns   |

| <b>t</b> ehwh     | twн             | WE Hold Time            | WE Hold Time                |      | 0   | ns   |

| <b>t</b> eleh     | t <sub>CP</sub> | CE Pulse Width          |                             | Min. | 50  | ns   |

| <b>t</b> ehel     | tсрн            | CE Pulse Width          | High                        | Min. | 30  | ns   |

| <b>t</b> whwh1    | <b>t</b> wнwн1  | Byte Programmir         | ng Operation                | Тур. | 8   | μs   |

| twhwh2            | twhwh2          | Sector Erase Op         | eration (Note)              | Тур. | 1   | sec  |

| _                 | tvcs            | Vcc Setup Time          |                             | Min. | 50  | μs   |

| _                 | t <sub>RB</sub> | Recover Time From RY/BY |                             | Min. | 0   | ns   |

| _                 | <b>t</b> RP     | RESET Pulse Width       |                             | Min. | 500 | ns   |

| _                 | tкн             | RESET Hold Tim          | RESET Hold Time Before Read |      | 500 | ns   |

| —                 | <b>t</b> BUSY   | Program/Erase \         | /alid to RY/BY Delay        | Min. | 90  | ns   |

Note: This does not include the preprogramming time.

### ■ ERASE AND PROGRAMMING PERFORMANCE

| Deremeter             | Limits  |      | Unit  | Comment |                                            |

|-----------------------|---------|------|-------|---------|--------------------------------------------|

| Parameter             | Min.    | Тур. | Max.  | Unit    | Comment                                    |

| Sector Erase Time     | _       | 1    | 15    | sec     | Excludes programming time prior to erasure |

| Byte Programming Time | _       | 8    | 3600  | μs      | Excludes system-level<br>overhead          |

| Chip Programming Time | _       | 6    | T.B.D | sec     | Excludes system-level<br>overhead          |

| Erase/Program Cycle   | 100,000 | —    |       | Cycles  |                                            |

### ■ TSOP PIN CAPACITANCE

| Parameter<br>Symbol | Parameter Description   | Test Setup          | Тур. | Max. | Unit |

|---------------------|-------------------------|---------------------|------|------|------|

| CIN                 | Input Capacitance       | V <sub>IN</sub> = 0 | 7    | 8    | pF   |

| Соит                | Output Capacitance      | Vout = 0            | 8    | 10   | pF   |

| CIN2                | Control Pin Capacitance | V <sub>IN</sub> = 0 | 9    | 11   | pF   |

**Note:** Test conditions  $T_A = 25^{\circ}C$ , f = 1.0 MHz

### ■ 40 SON PIN CAPACITANCE

| Parameter<br>Symbol | Parameter Description   | Test Setup          | Тур. | Max. | Unit |

|---------------------|-------------------------|---------------------|------|------|------|

| CIN                 | Input Capacitance       | V <sub>IN</sub> = 0 | 7    | 8    | pF   |

| Соит                | Output Capacitance      | Vout = 0            | 8    | 10   | pF   |

| CIN2                | Control Pin Capacitance | VIN = 0             | 9    | 11   | pF   |

**Note:** Test conditions  $T_A = 25^{\circ}C$ , f = 1.0 MHz

# FUJITSU LIMITED

For further information please contact:

#### Japan

FUJITSU LIMITED Corporate Global Business Support Division Electronic Devices KAWASAKI PLANT, 4-1-1, Kamikodanaka Nakahara-ku, Kawasaki-shi Kanagawa 211-8588, Japan Tel: (044) 754-3763 Fax: (044) 754-3329

http://www.fujitsu.co.jp/

#### North and South America

FUJITSU MICROELECTRONICS, INC. Semiconductor Division 3545 North First Street San Jose, CA 95134-1804, USA Tel: (408) 922-9000 Fax: (408) 922-9179

Customer Response Center *Mon. - Fri.: 7 am - 5 pm (PST)* Tel: (800) 866-8608 Fax: (408) 922-9179

http://www.fujitsumicro.com/

#### Europe

FUJITSU MIKROELEKTRONIK GmbH Am Siebenstein 6-10 D-63303 Dreieich-Buchschlag Germany Tel: (06103) 690-0 Fax: (06103) 690-122

http://www.fujitsu-ede.com/

#### **Asia Pacific**

FUJITSU MICROELECTRONICS ASIA PTE LTD #05-08, 151 Lorong Chuan New Tech Park Singapore 556741 Tel: (65) 281-0770 Fax: (65) 281-0220

http://www.fmap.com.sg/

F9803 © FUJITSU LIMITED Printed in Japan All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information and circuit diagrams in this document presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

FUJITSU semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.). CAUTION:

Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with FUJITSU sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Control Law of Japan, the prior authorization by Japanese government should be required for export of those products from Japan.